Floating-point mixed-radix FFT core generation for FPGA and comparison with GPU and CPU | Semantic Scholar

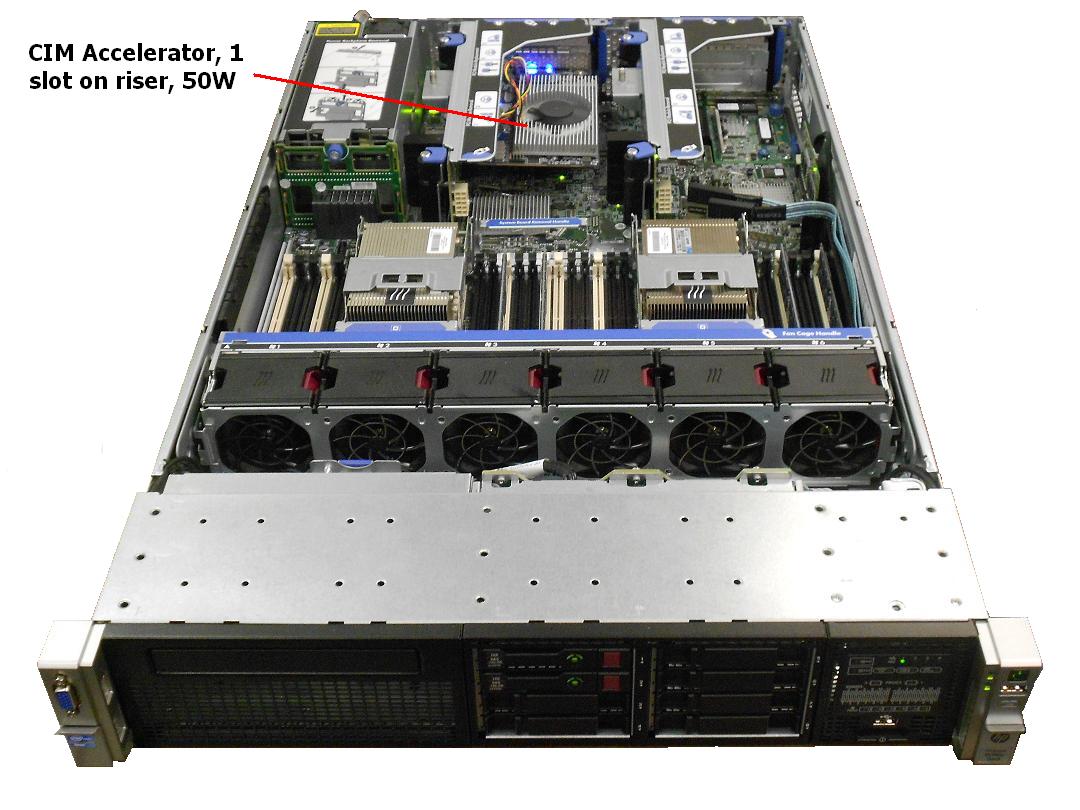

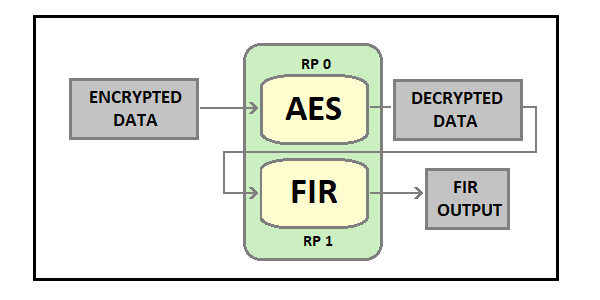

Solving integrated hardware accelerator challenges - Research Articles - Research Collaboration and Enablement - Arm Community

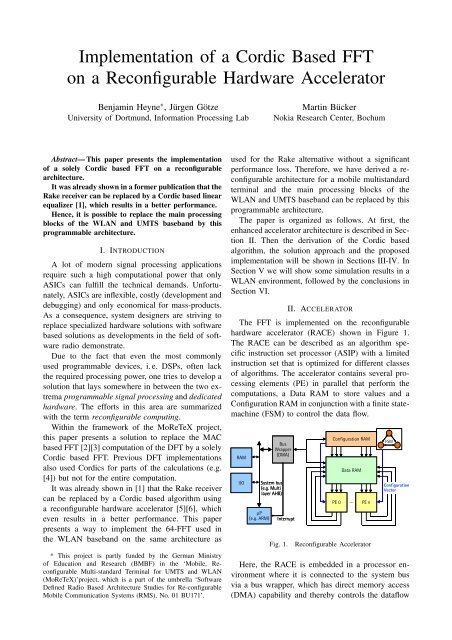

An Efficient FPGA Architecture for Reconfigurable FFT Processor Incorporating an Integration of an Improved CORDIC and Radix-2r Algorithm | SpringerLink

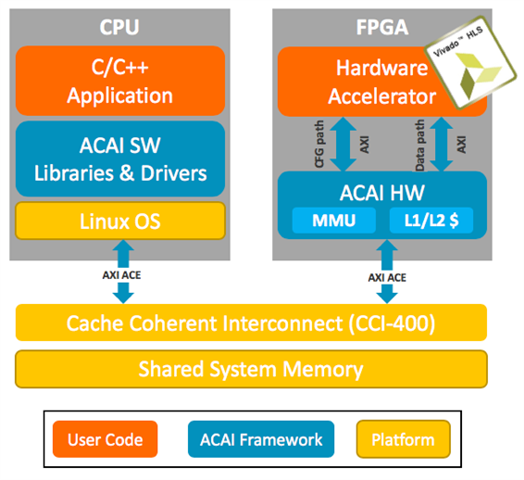

Architecture ZC702 with the FFT IP as a hardware accelerator component... | Download Scientific Diagram

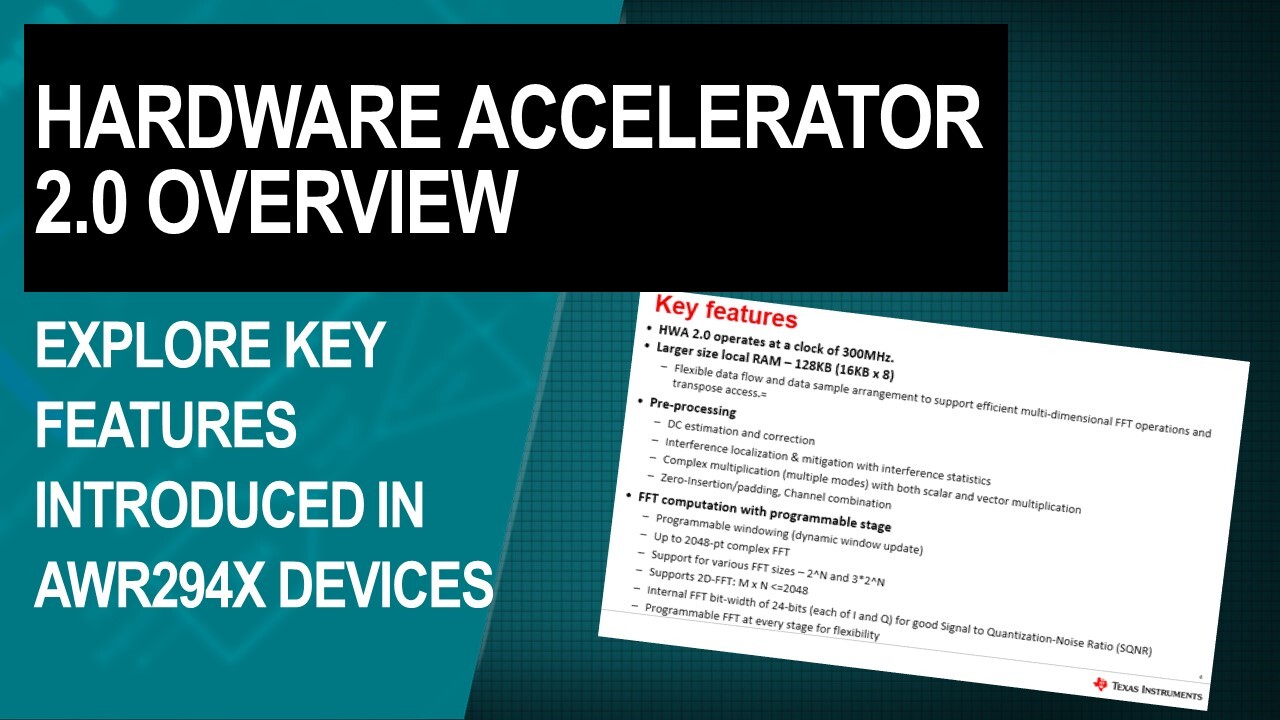

![PDF] CRAFFT: High Resolution FFT Accelerator In Spintronic Computational RAM | Semantic Scholar PDF] CRAFFT: High Resolution FFT Accelerator In Spintronic Computational RAM | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/8eab8699727bd1935d46fde93c63cb570babad1e/3-Figure4-1.png)